Sigma-Delta DAC

Ordnung 1

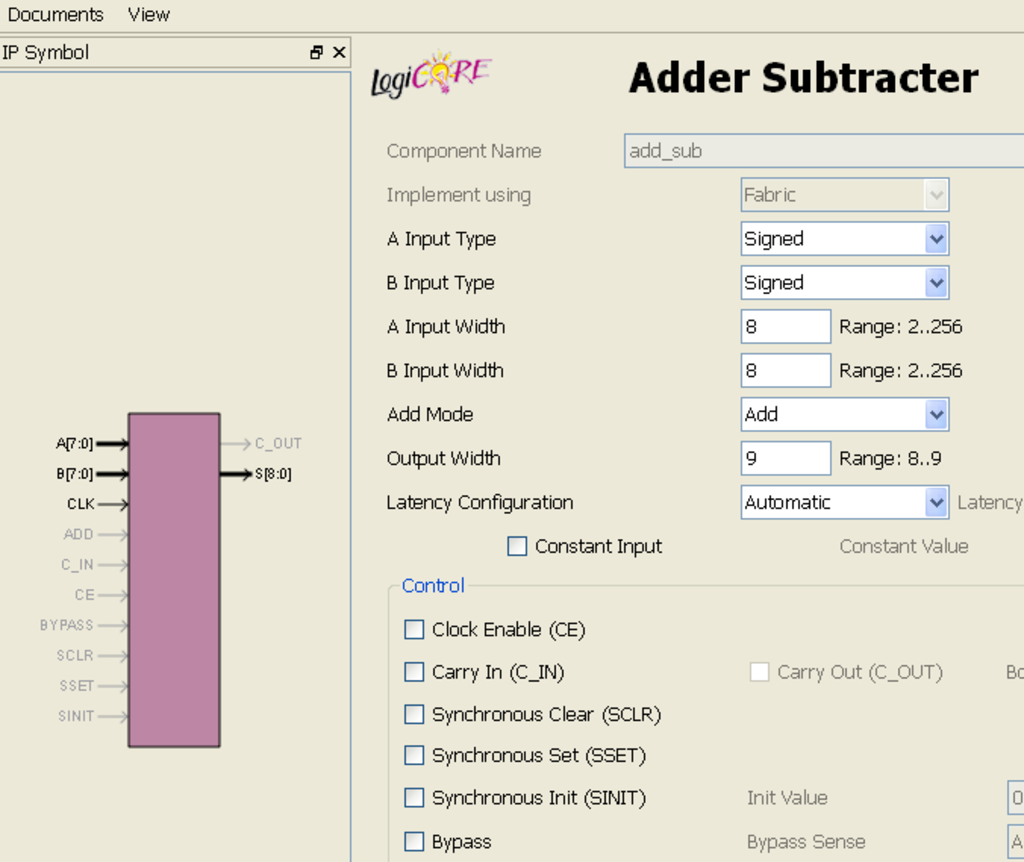

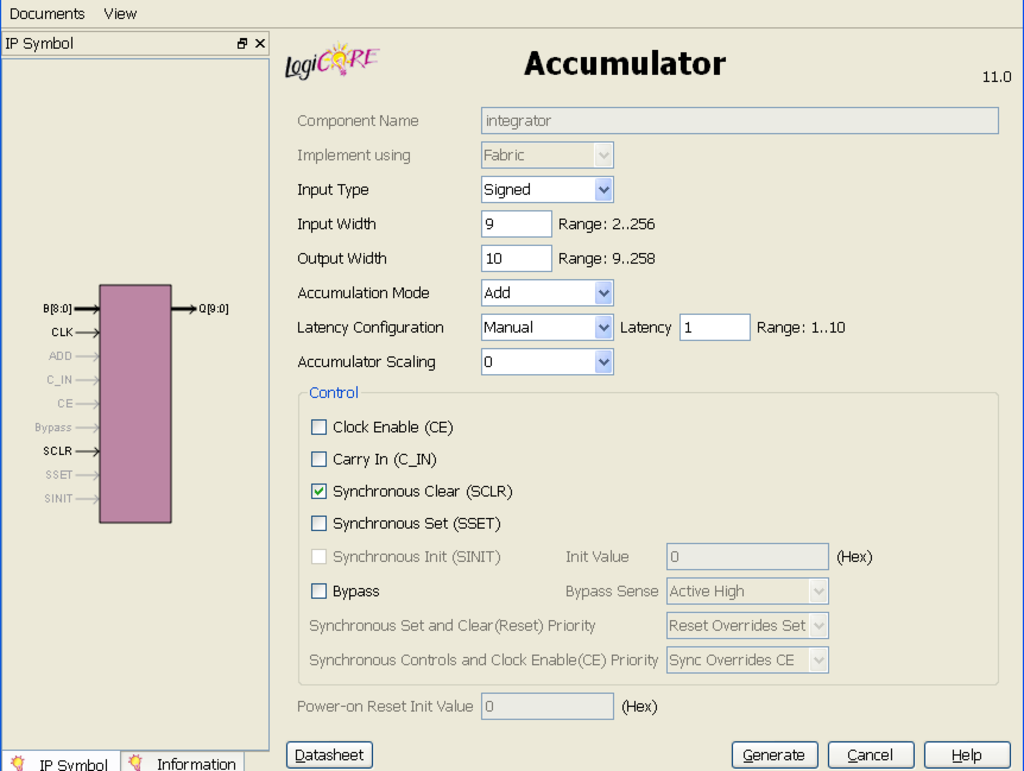

XILINX ISE Webpack Komponente

Top Sheet

Das Modell für den DDC enthält die Ausgabe in ein Logfile um die Simulationsergebnisse in LTSpice einbinden zu können

Der aktuelle Wert wird zwischengespeichert und verzögert noch einmal ausgegeben damit man Rechteck-Impulse kriegt: also 1ns 0, 1.1ns 1, 2ns 1, 2.1ns 0 usw.

if s1(9)'event then

write(txt, now);

write(txt, string'(" "));

write(txt,conv_integer(old_output));

writeline(log_file, txt);

tim := now+del;

write(txt, tim);

write(txt, string'(" "));

write(txt,conv_integer(s1(9)));

writeline(log_file, txt);

end if;

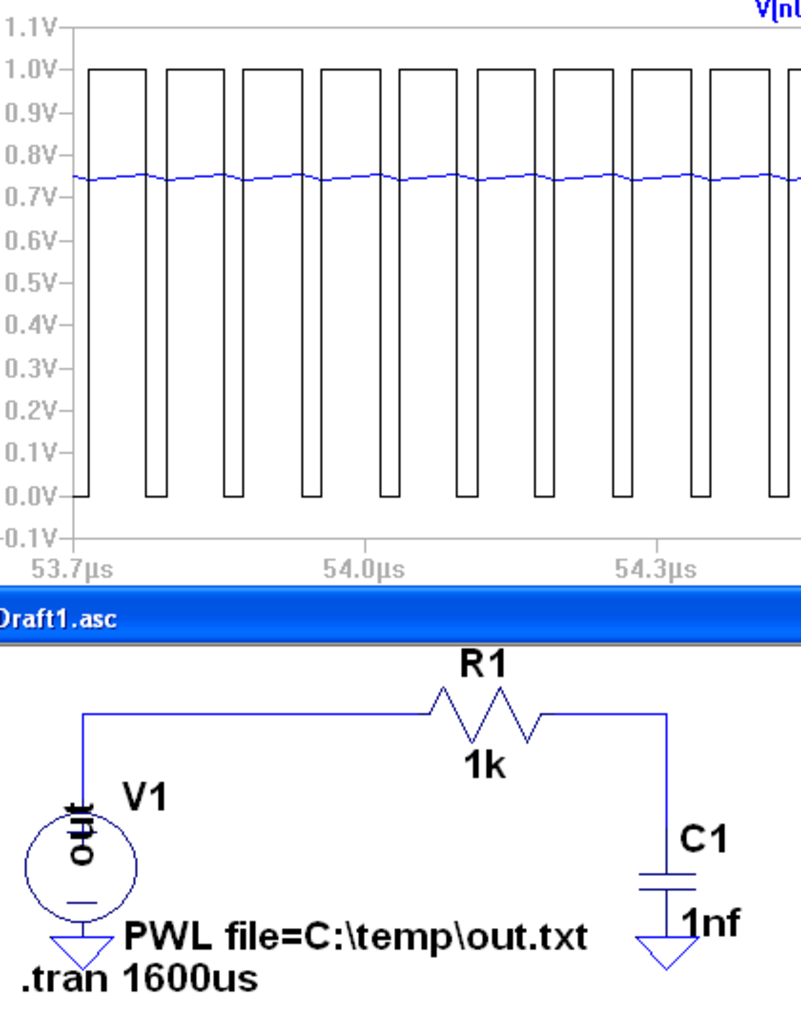

Simulationsergebnisse in LTSpice

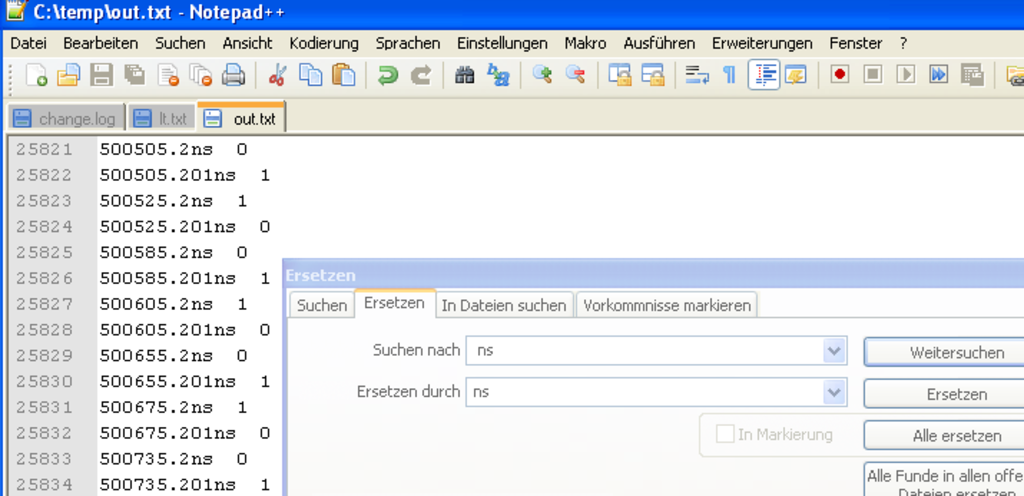

Das Logfile muss editiert werden, am besten in einen guten Texteditor laden und S&R „ ns“ muss ersetzt werden durch „ns“ (ein Leerzeichen entfernen)

Logfile in Voltage-Source einbinden

das Ergebnis ist eine Gleichspannung