Beispiele am Coolrunner II Demoboard

Beispiele am Coolrunner II Demoboard

Neues Projekt anlegen als Schematic

die VHDL-Module einbinden (Add Source as Copy)

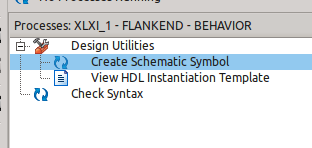

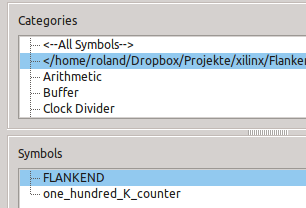

von den Modulen ein Schaltsymbol erstellen

Top-Sheet Schaltplan zeichnen und Module einbinden

Es gibt mehrere VHDL-Module in der Coolrunner-Demo die in den Projekten verwendet werden können:

Clock-Teiler

7-Seg Decoder

LCD-Modul

Anmerkung!

Clock

Input auf P38, dann in einen Teiler rein; durch Jumper JP1 auf dem Demoboard umschaltbar 0.1Hz 1Hz 10Hz?Reset

die Tasten des Demoboards sind statisch auf 1, daher Reset; Achtung: Statecad Reset ist default auf aktivdas Constraint-File (top.ucf) wird eingebunden und editiert

#kner 2012

net clk loc = p38 | bufg=clk; #clockbuffer

net led loc = p64; #LD3 Disp A3

net clkled loc = p66; #LD3 Disp A2

net in1led loc = p68; #LD3 Disp A1

net rst loc = p143; # assign reset to be BTN0

net in1 loc = p94; # assign clock enable to be BTN1

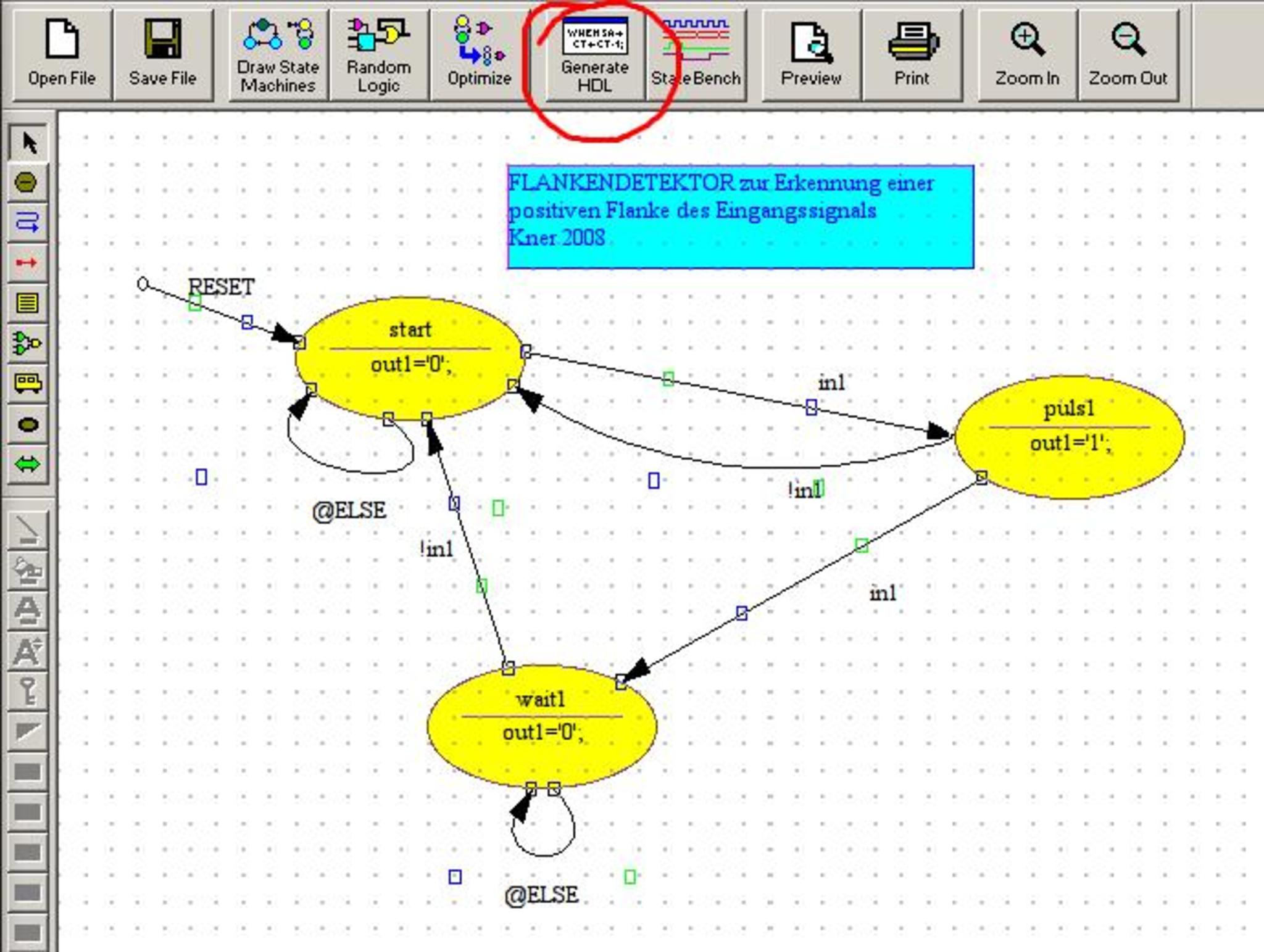

StateCad-Projekte

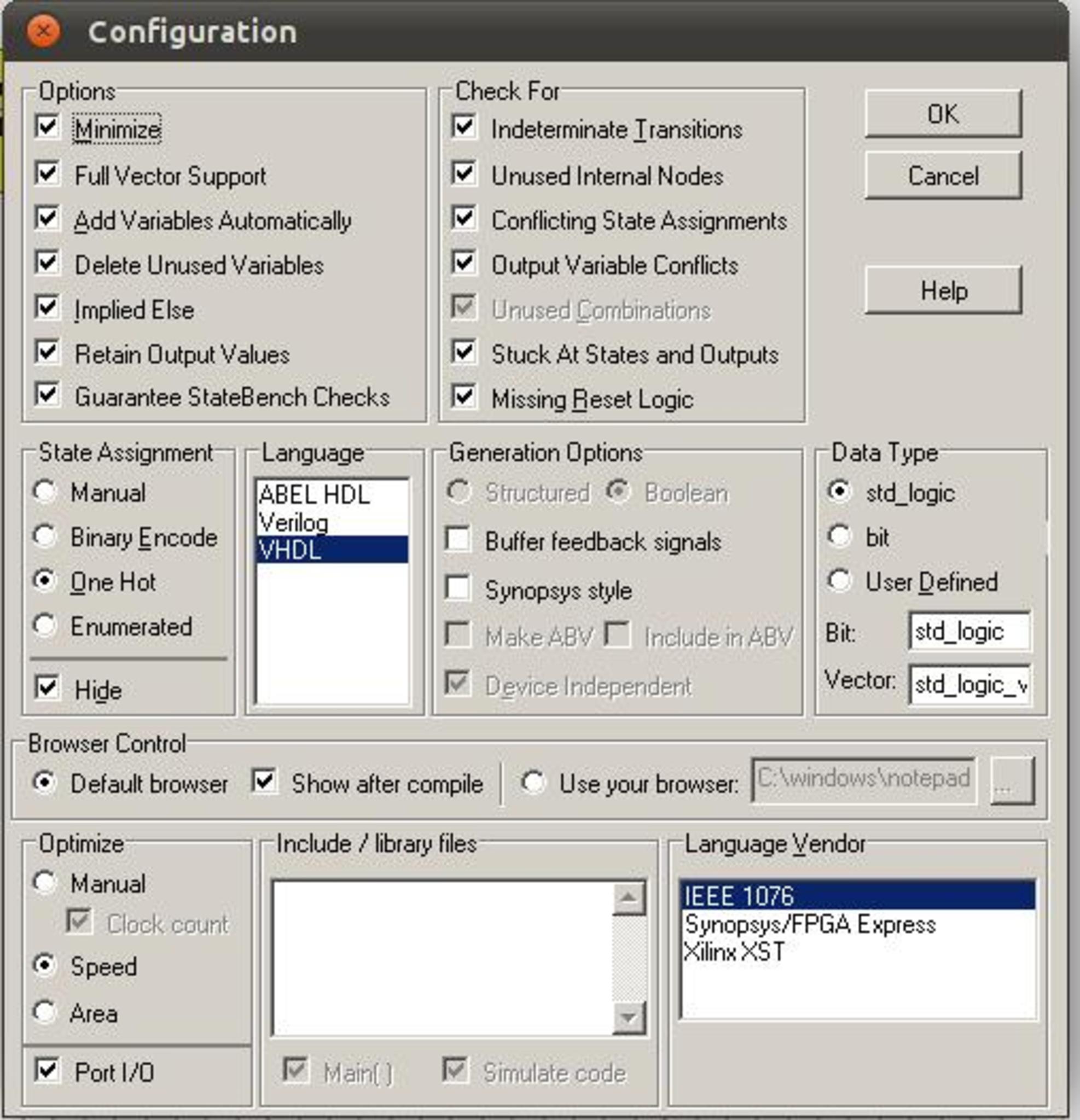

Statecad konfigurieren: Language Vendor auf IEEE

Statecad erzeugt das HDL-File: Generate HDL; Achtung auf die Polarität von Reset (hier wäre !Reset besser, weil das Coolrunner-Demoboard die Tasten aktive LOW verlötet hat

HDL in das ISE Projekt importieren, Schaltplan erzeugen

Kompilieren

Kner

2011